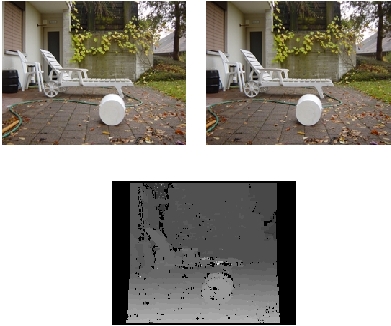

Top images: two horizontally displaced camera images of a scene

Bottom image: The corresponding depth map with light colors for near regions and dark colors for distant objects

Since calculating depth maps is a computationally intensive task, the idea of an ASIC doing the job real-time came up. In this way, stereo vision could be used for dynamic scenes like street traffic, collision avoidance or mobile robot navigation.

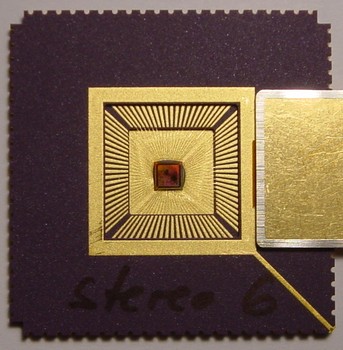

The Chip

The ASIC works on images of size 256*192 with 256 gray scales. Running with 75MHz it achieves more than 50 frames per second (fps), which corresponds to roughly 18 GOps. It occupies an area of only 2.56mm^2 on an UMC 0.25um 5metal process.

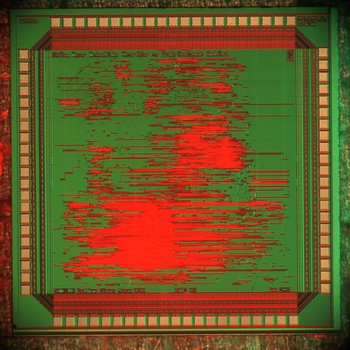

Left: image of opened chip package. Right: Microscopic view of the silicon

last update: 22.2.04 Stephan Moser